流水线 CPU 准备实现的指令

共 31 条 MIPS 指令,包含了大多数基本指令操作。

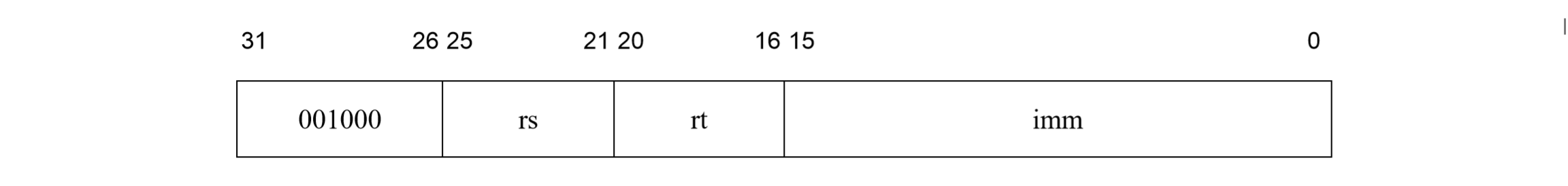

ADDI

将寄存器 rs 的值与有符号扩展至 32 位的立即数 imm 相加,结果写入 rt 寄存器中。如果产生溢出,则触发整型溢出例外(IntegerOverflow)。

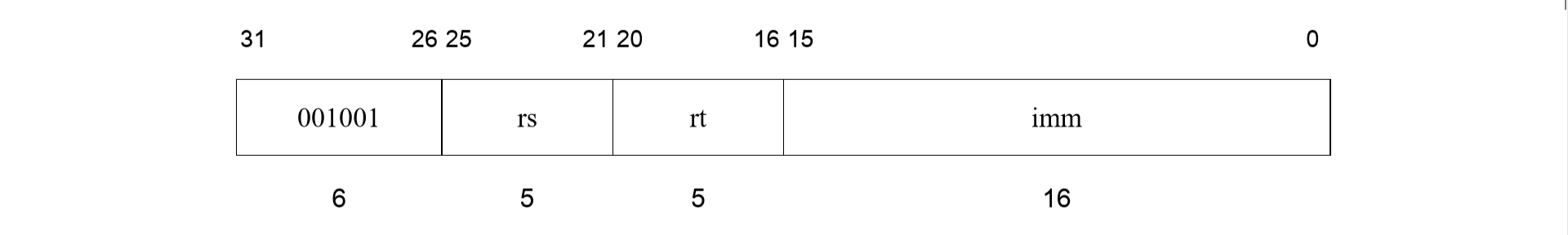

ADDIU

将寄存器 rs 的值与有符号扩展至 32 位的立即数 imm 相加,结果写入 rt 寄存器中。

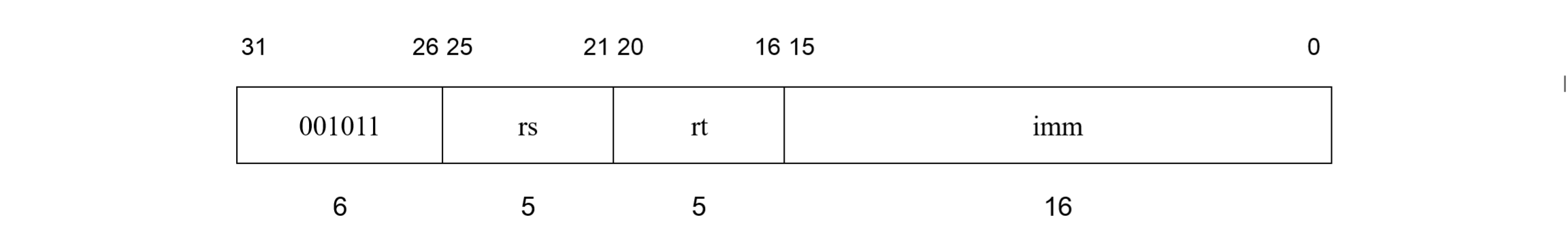

SLTIU

将寄存器 rs 的值与 有符号扩展至 32 位的立即数 imm 进行无符号数比较,如果寄存器 rs 中的值小,则寄存器 rt 置 1;否则寄存器 rt 置 0。

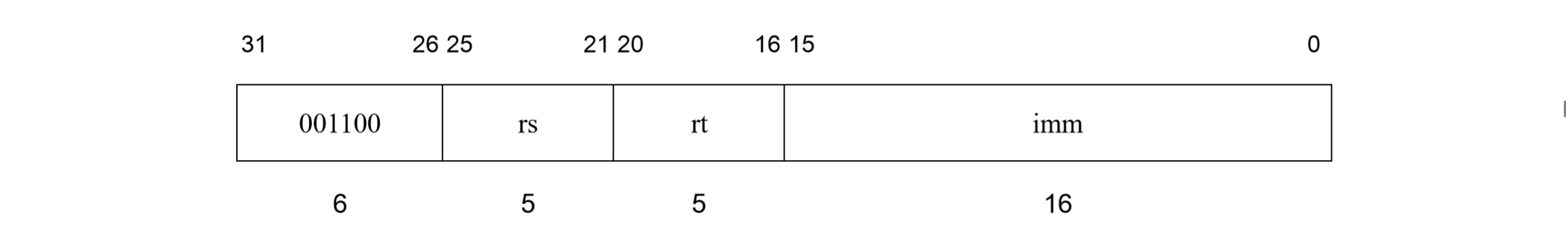

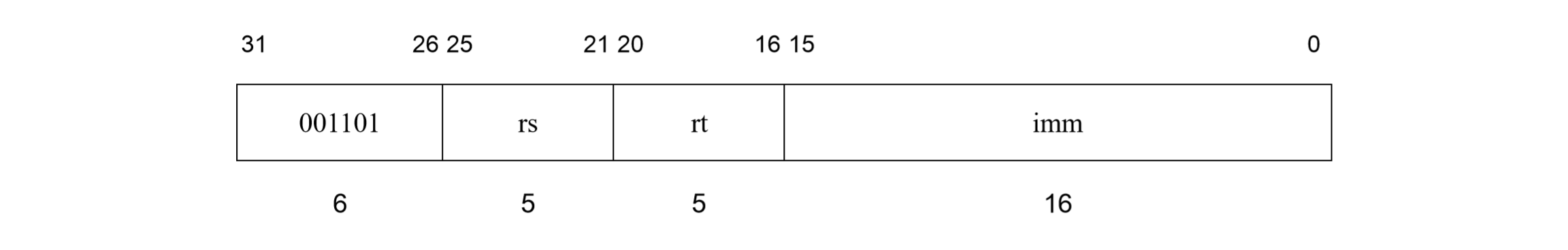

ANDI

寄存器 rs 中的值与 0 扩展至 32 位的立即数 imm 按位逻辑与,结果写入寄存器 rt 中。

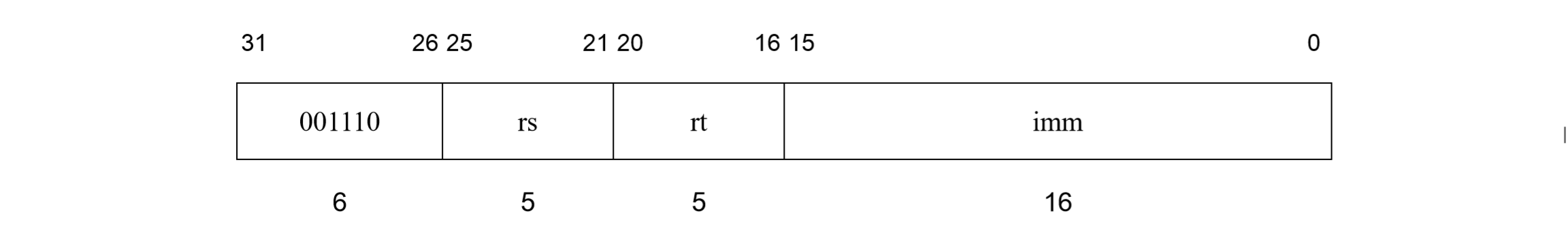

ORI

寄存器 rs 中的值与 0 扩展至 32 位的立即数 imm 按位逻辑或,结果写入寄存器 rt 中。

XORI

寄存器 rs 中的值与 0 扩展至 32 位的立即数 imm 按位逻辑异或,结果写入寄存器 rt 中。

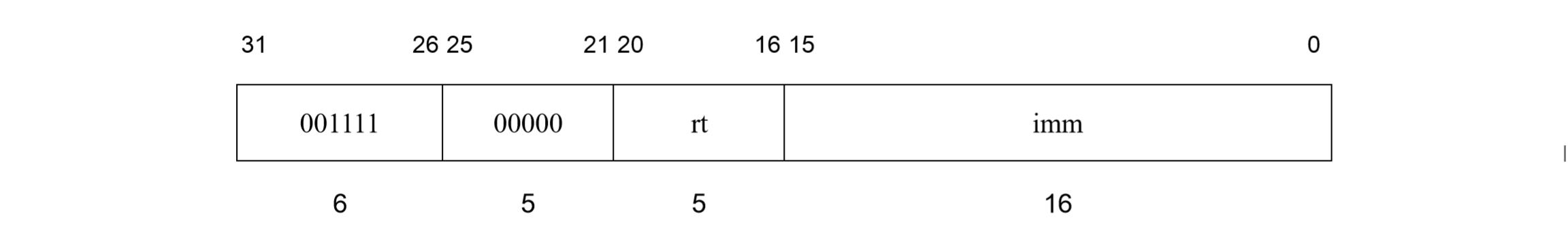

LUI

将 16 位立即数 imm 写入寄存器 rt 的高 16 位,寄存器 rt 的低 16 位置 0。

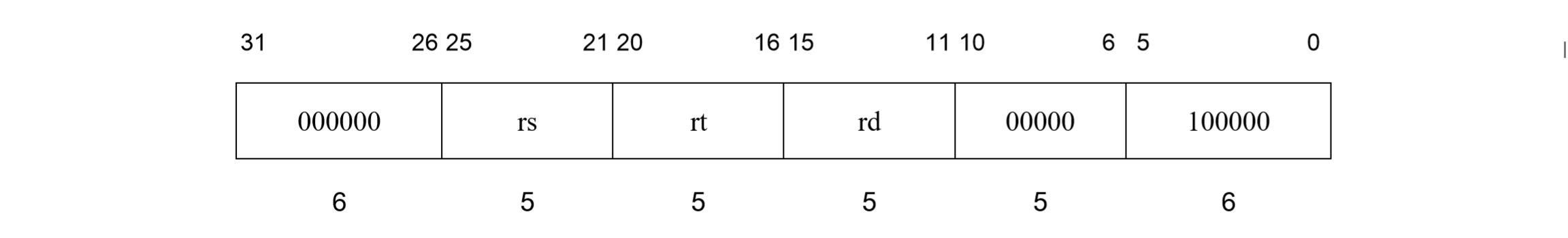

ADD

将寄存器 rs 的值与寄存器 rt 的值相加,结果写入寄存器 rd 中。如果产生溢出,则触发整型溢出例外(IntegerOverflow)。

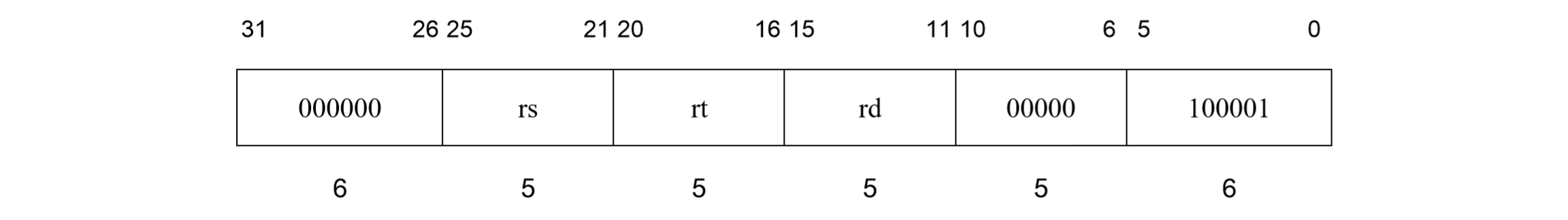

ADDU

将寄存器 rs 的值与寄存器 rt 的值相加,结果写入 rd 寄存器中。

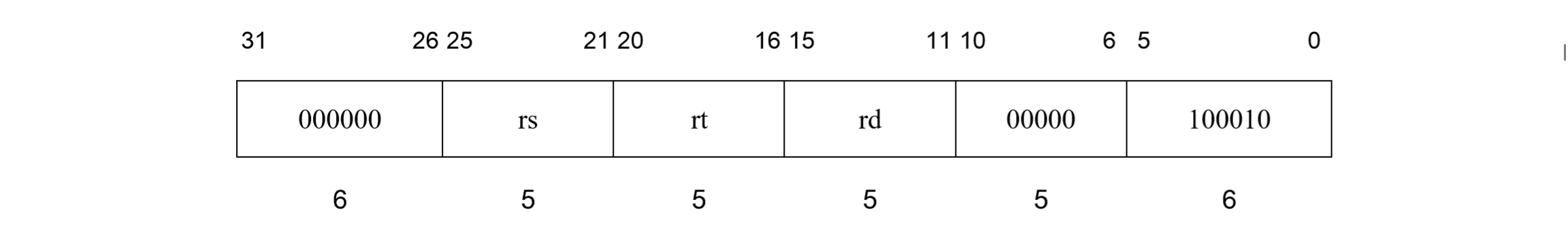

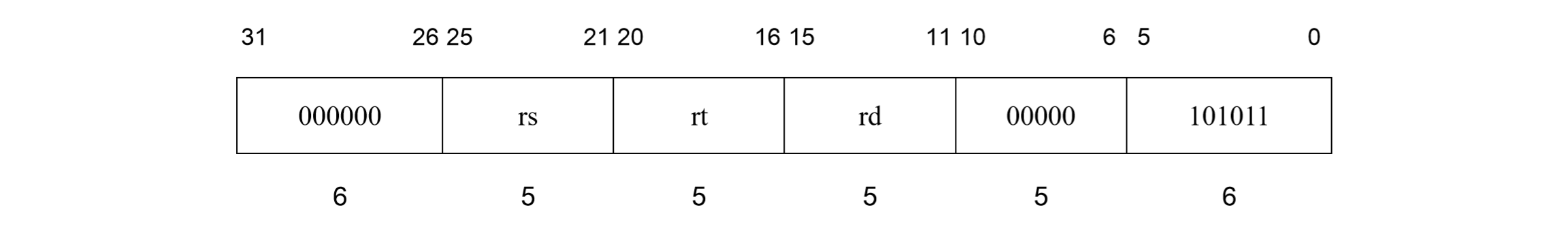

SUB

将寄存器 rs 的值与寄存器 rt 的值相减,结果写入 rd 寄存器中。如果产生溢出,则触发整型溢出例外(IntegerOverflow)。

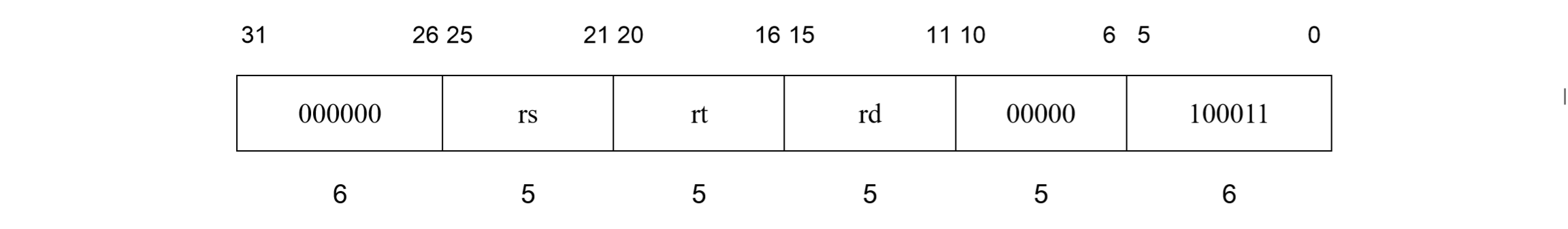

SUBU

将寄存器 rs 的值与寄存器 rt 的值相减,结果写入 rd 寄存器中。

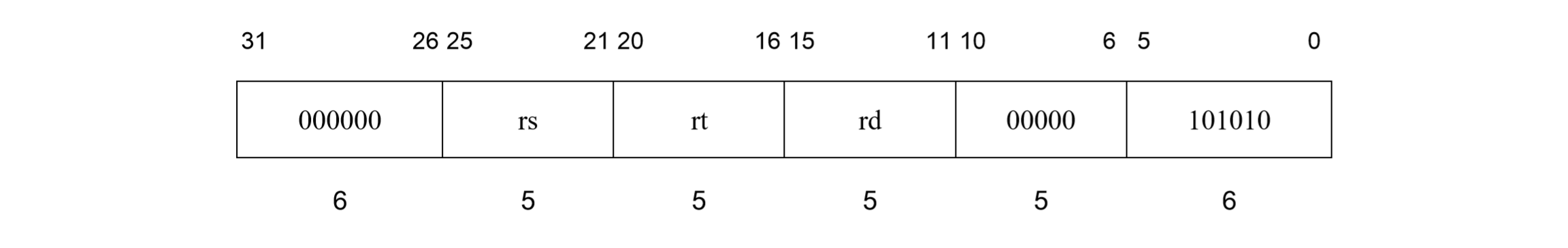

SLT

将寄存器 rs 的值与寄存器 rt 中的值进行有符号数比较,如果寄存器 rs 中的值小,则寄存器 rd 置 1;否则寄存器 rd 置 0。

SLTU

将寄存器 rs 的值与寄存器 rt 中的值进行无符号数比较,如果寄存器 rs 中的值小,则寄存器 rd 置 1;否则寄存器 rd 置 0。

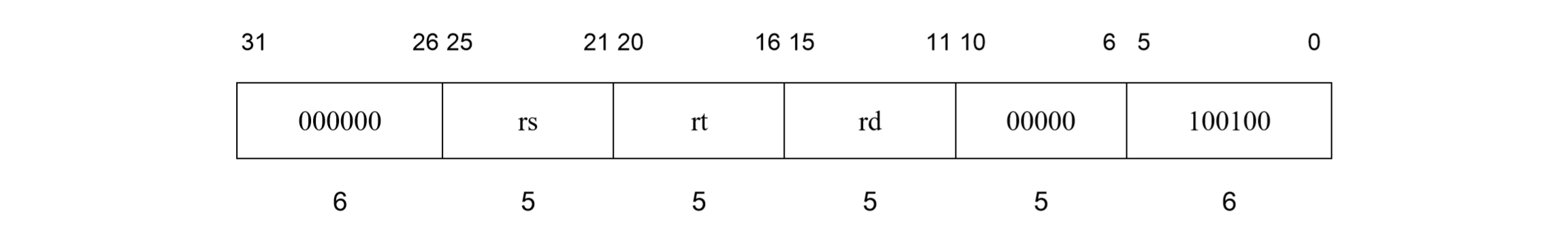

AND

寄存器 rs 中的值与寄存器 rt 中的值按位逻辑与,结果写入寄存器 rd 中。

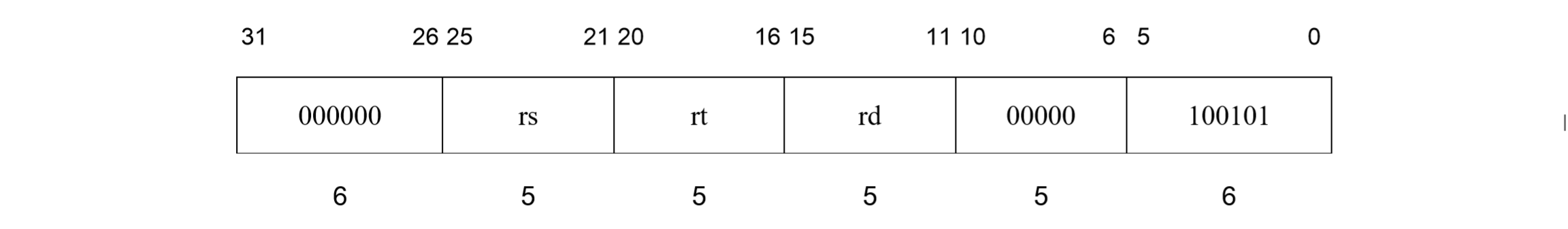

OR

寄存器 rs 中的值与寄存器 rt 中的值按位逻辑或,结果写入寄存器 rd 中。

NOR

寄存器 rs 中的值与寄存器 rt 中的值按位逻辑或非,结果写入寄存器 rd 中。

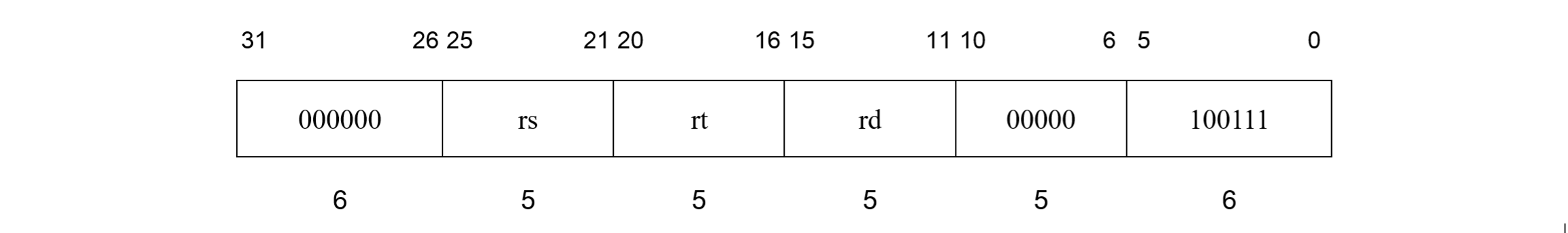

XOR

寄存器 rs 中的值与寄存器 rt 中的值按位逻辑异或,结果写入寄存器 rd 中。

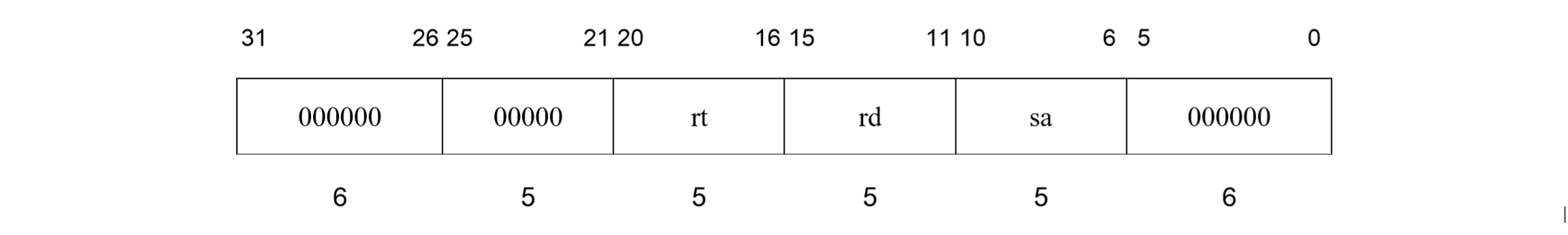

SLL

由立即数 sa 指定移位量,对寄存器 rt 的值进行逻辑左移,结果写入寄存器 rd 中。

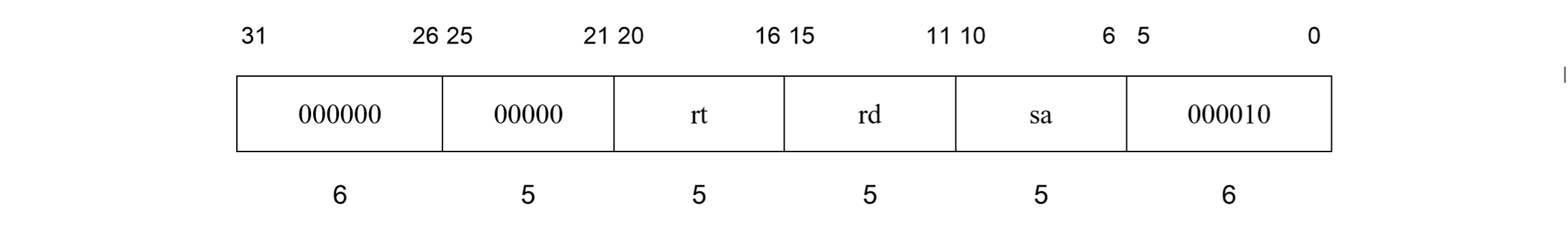

SRL

由立即数 sa 指定移位量,对寄存器 rt 的值进行逻辑右移,结果写入寄存器 rd 中。

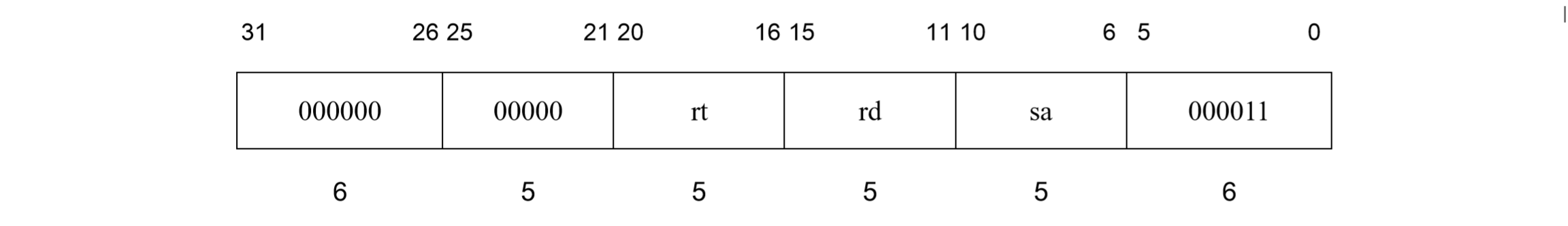

SRA

由立即数 sa 指定移位量,对寄存器 rt 的值进行算术右移,结果写入寄存器 rd 中。

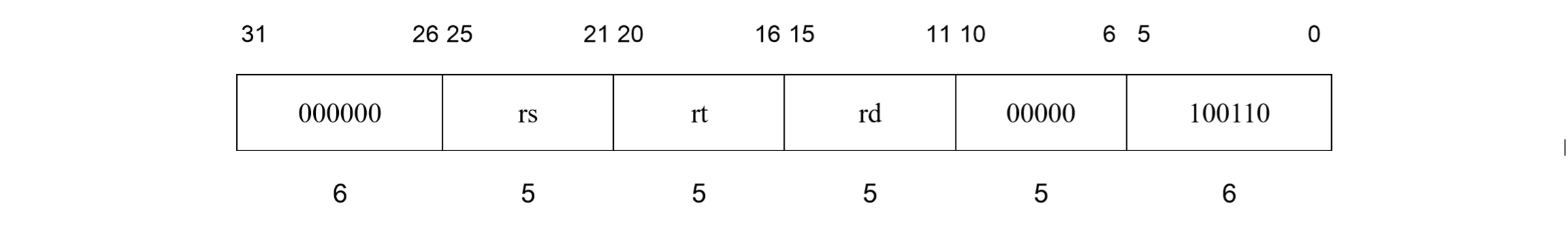

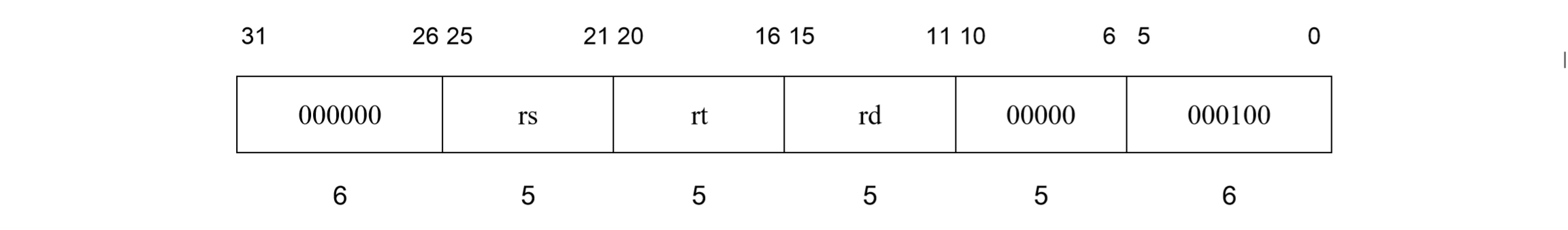

SLLV

由寄存器 rs 中的值指定移位量,对寄存器 rt 的值进行逻辑左移,结果写入寄存器 rd 中。

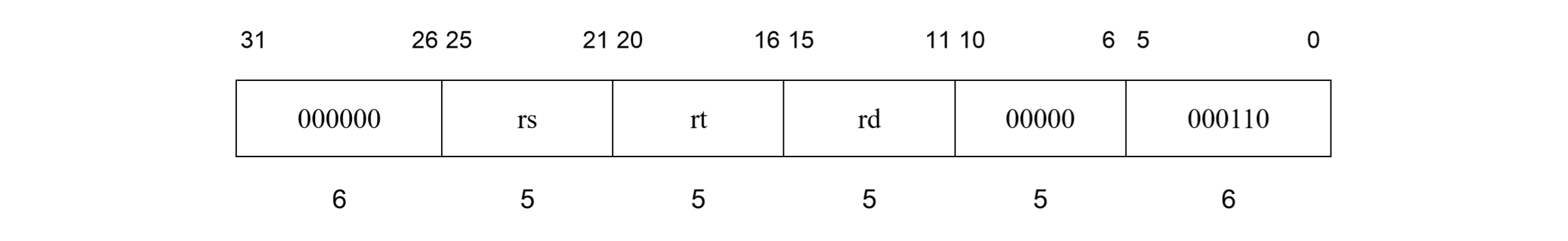

SRLV

由寄存器 rs 中的值指定移位量,对寄存器 rt 的值进行逻辑右移,结果写入寄存器 rd 中。

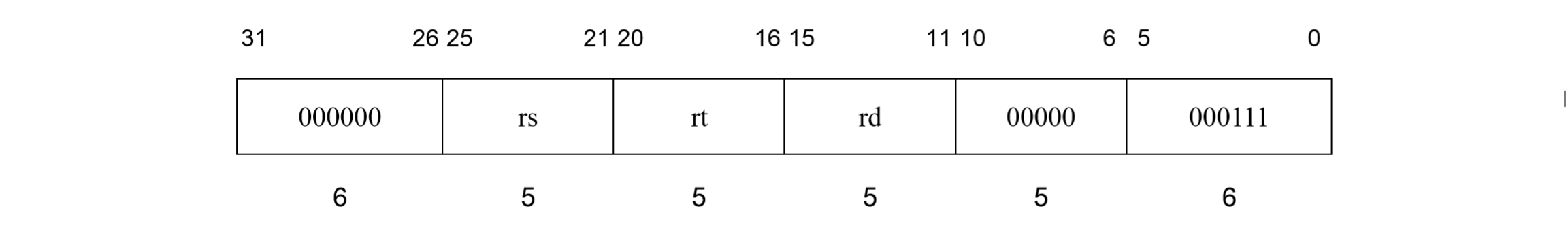

SRAV

由寄存器 rs 中的值指定移位量,对寄存器 rt 的值进行算术右移,结果写入寄存器 rd 中。

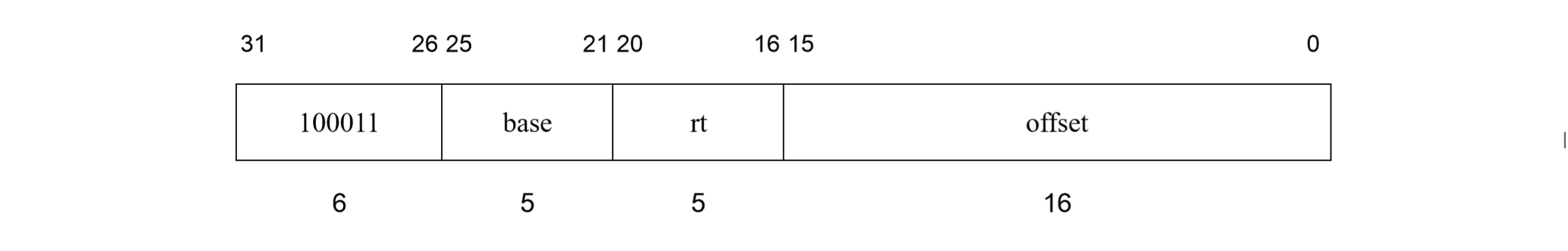

LW

将 base 寄存器的值加上符号扩展后的立即数 offset 得到访存的虚地址,如果地址不是 4 的 整数倍则触发地址错例外,否则据此虚地址从存储器中读取连续 4 个字节的值并进行符号 扩展,写入到 rt 寄存器中。

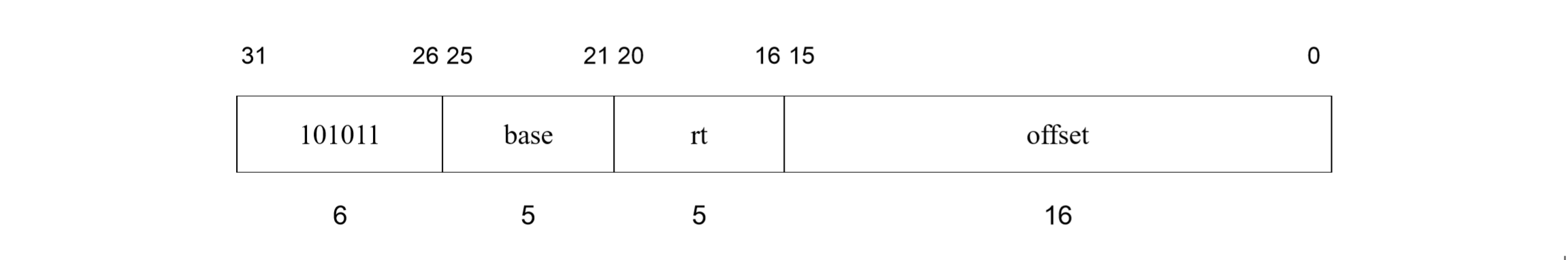

SW

将 base 寄存器的值加上符号扩展后的立即数 offset 得到访存的虚地址,如果地址不是 4 的 整数倍则触发地址错例外,否则据此虚地址将 rt 寄存器存入存储器中。

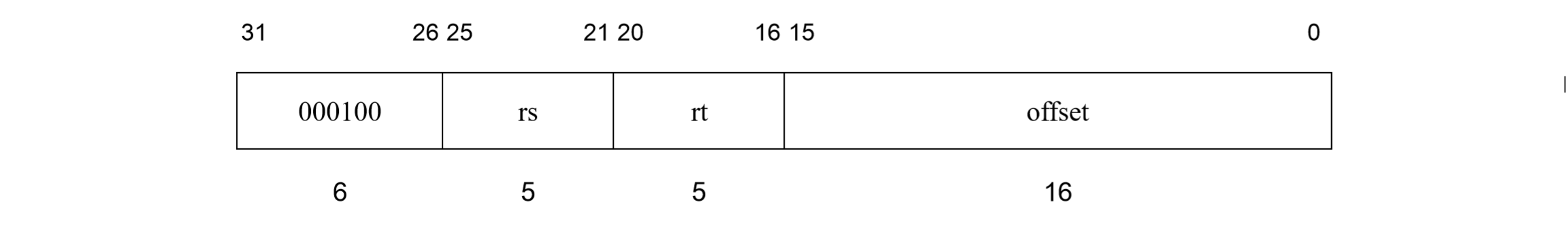

BEQ

如果寄存器 rs 的值等于寄存器 rt 的值则转移,否则顺序执行。转移目标由立即数 offset 左 移 2 位并进行有符号扩展的值加上该分支指令对应的延迟槽指令的 PC 计算得到。

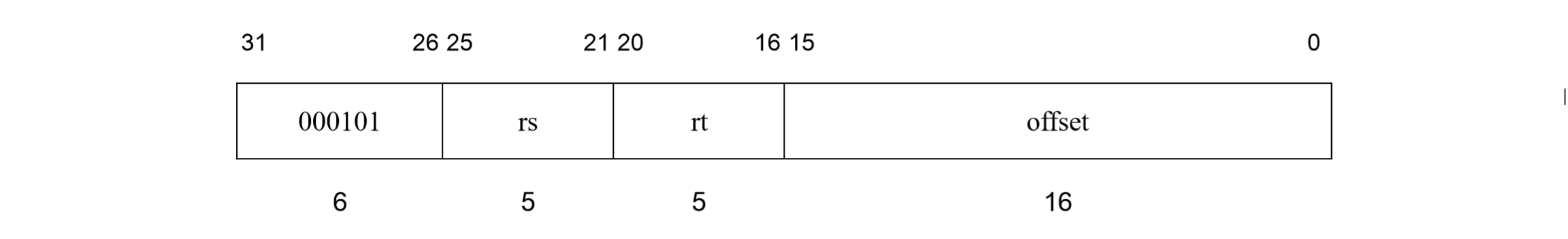

BNE

如果寄存器 rs 的值不等于寄存器 rt 的值则转移,否则顺序执行。转移目标由立即数 offset 左移 2 位并进行有符号扩展的值加上该分支指令对应的延迟槽指令的 PC 计算得到。

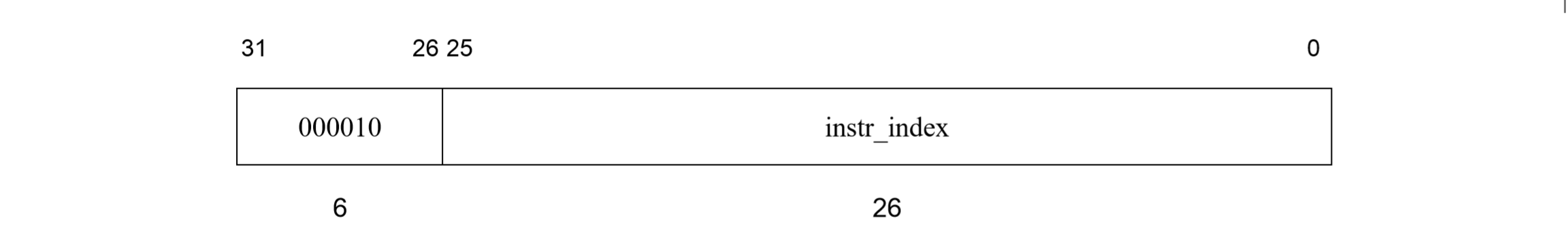

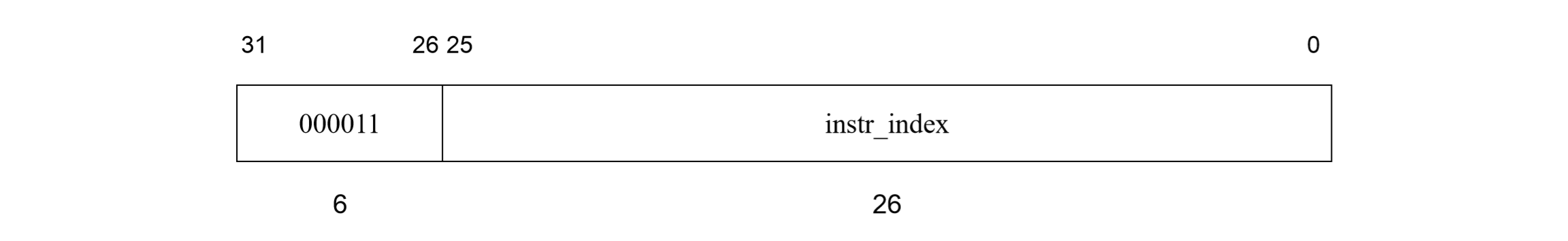

J

无条件跳转。跳转目标由该分支指令对应的延迟槽指令的 PC 的最高 4 位与立即数 instr_index 左移 2 位后的值拼接得到。

JAL

无条件跳转。跳转目标由该分支指令对应的延迟槽指令的 PC 的最高 4 位与立即数 instr_index 左移 2 位后的值拼接得到。同时将该分支对应延迟槽指令之后的指令的 PC 值保存至第 31 号通用寄存器中。

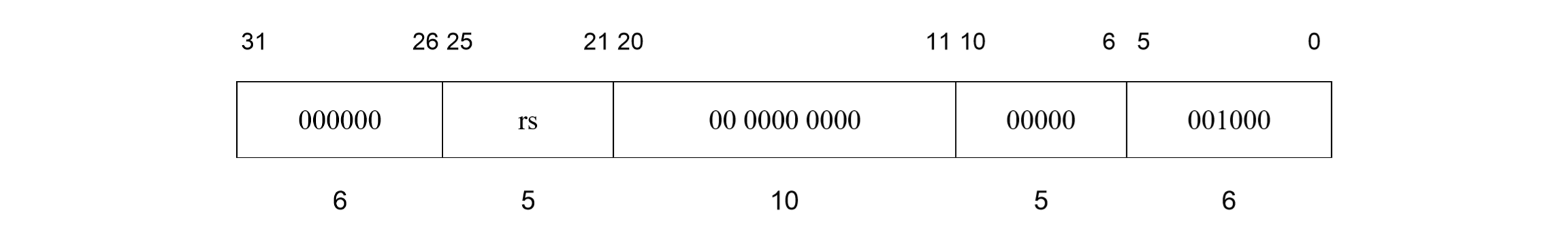

JR

无条件跳转。跳转目标为寄存器 rs 中的值。

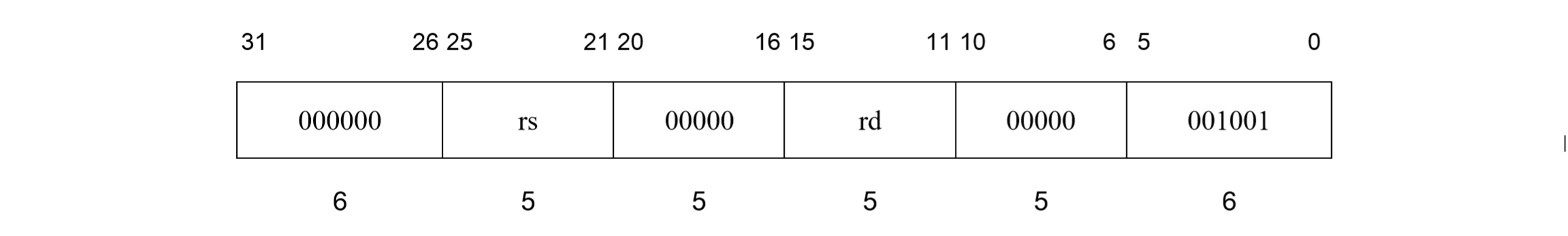

JALR

无条件跳转。跳转目标为寄存器 rs 中的值。同时将该分支对应延迟槽指令之后的指令的 PC 值保存至寄存器 rd 中。